MCU0.0如何看时钟树

时钟树(Clock Tree)

时钟树(Clock Tree)是嵌入式系统中用于管理和分配时钟信号的重要组成部分。理解时钟树对于正确配置和优化系统的时钟架构至关重要。注意最终我们要得到的是RTC(实时时间)与SYSCLK(系统时间)。

1 . 查阅数据手册和参考手册

首先,查阅所使用的微控制器或处理器的数据手册(Datasheet)和参考手册(Reference Manual)是了解时钟树结构的关键步骤。这些文档通常包含详细的时钟树图以及相关的寄存器配置信息。

2 . ESP32的时钟树简图

我们先以ESP32的时钟树简图为例。

时钟树图通常是一个层次结构图,展示了从时钟源到各个系统模块的时钟分配路径。时钟树图通常包括以下几个部分:

时钟源:如外部晶振(HSE)、内部高频RC振荡器(HSI)、低频外部晶振(LSE)、内部低频RC振荡器(LSI)等,以上为较为通用的叫法。

ESP32-S3 的时钟主要来源于振荡器(oscillator,OSC)、 RC 振荡电路和 PLL 时钟生成电路。

高性能时钟:主要为 CPU 和数字外设提供工作时钟

PLL_CLK:320 MHz 或 480 MHz 内部 PLL 时钟

ESP32中的PLL(Phase-Locked Loop,锁相环)时钟是一种用于产生精确且稳定的时钟信号的技术。PLL是一种常用的频率合成器,它可以用来生成一个与参考频率成固定倍数关系的输出频率。在ESP32中,PLL被广泛用于产生各种内部和外部时钟信号,以满足不同模块的时钟需求。可以将PLL理解为一种特殊的倍频器器。

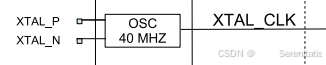

– XTAL_CLK:40 MHz 外部晶振时钟

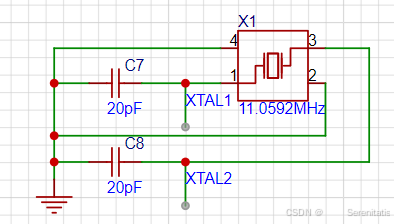

外部晶振电路一般长这样(图中是一个51晶振):

- 低功耗时钟,主要为 RTC 模块以及部分处于低功耗模式的外设提供工作时钟

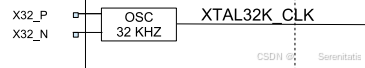

XTAL32K_CLK:32 kHz 外部晶振时钟

RC_FAST_CLK:内置快速 RC 振荡器时钟,频率可调节(通常为 17.5 MHz)

RC_FAST_DIV_CLK:内置快速 RC 振荡器分频时钟,由内置快速 RC 振荡器时钟经 256 分频生成

RC_SLOW_CLK:内置慢速 RC 振荡器,频率可调节(通常为 136 kHz)

- 分频器:它的功能是将输入信号的频率降低到一个预定的比例。如AHB、APB1、APB2等分频器。

在ESP32中分频器一般用DIV表示,有些分频器可调有些则是固定的。

- 数据选择器:顾名思义就是用来选择数据的,在这用用来选择时钟的来源,和分频器一样有些有硬件控制有些则受到软件控制。

- 时钟输出:分配给各个系统模块的时钟信号。

这里分别是给CPU的时钟,给WIFI和蓝牙的时钟,给外设的时钟。当然这里的外设包括UART和外围的传感器设备。对于外围的传感器只有正连接了时钟输出引脚的才是真正的同步。而对于很多设备其实只是进行了异步的数据交换。

这里我们在介绍一下RTC时钟。

RTC(Real-Time Clock,实时时钟)是一种专门设计用于保持时间的电路,通常集成在一个微小的芯片内。它可以在没有主电源的情况下工作,比如通过一块小型电池供电,从而允许设备即使在断电后也能维持时间信息。RTC在各种电子设备中都有广泛的应用,包括计算机、手机、嵌入式系统以及其他需要维护时间信息的产品。

2.1 RTC的主要功能和特性

时间保持:

- RTC的主要功能之一就是维持时间信息,即使在主电源关闭的情况下,RTC也可以继续计时。

低功耗:

- 由于RTC通常需要长时间运行,因此它被设计为非常低功耗的电路,可以在电池供电下持续工作多年。

独立电源:

- RTC通常由一块独立的小型电池(如CR2032)供电,这使得即使主电源断开,RTC仍能继续工作。

备份寄存器:

- 一些RTC模块提供了非易失性的备份寄存器,可以在主电源断开期间存储关键数据。

电源监控:

- 部分RTC还具有电源监控功能,可以在主电源电压下降时发出警告信号,提醒更换电池或采取其他措施。

1 .STM32的时钟树

下图为STM32F103的时钟树

可以看到输入里有两个挂着OUT的端口,当时通常情况下它们并不用于通过GPIO输出时钟而是用于辅助晶振工作的。

而MCO (Main Clock Output)才是主时钟输出,将 SYSCLK 输出到外部,用于同步外部设备或调试用途。其中OSC(Oscillator)用于外接晶振。PCLK2是APB2分频后的系统时钟。

接下来我们看注释

- HSI (High-Speed Internal): 内部高速时钟,通常是一个 RC 振荡器,提供大约 8 MHz 的时钟信号。

- HSE (High-Speed External): 外部高速时钟,通过外部晶振提供更精确的时钟信号,频率范围可以从几兆赫兹到几十兆赫兹。

- LSI (Low-Speed Internal): 内部低速时钟,通常是一个 RC 振荡器,提供约 40 kHz 的时钟信号。

- LSE (Low-Speed External): 外部低速时钟,通过外部晶振提供,通常用于实时时钟(RTC)功能,频率约为 32.768 kHz。对于32.768khz 2^15,经15此二分频得到1HZ

可以看到其实与ESP32类似我们继续看CSS

- CSS (Clock Security System):

CSS(时钟安全系统)是现代微控制器(MCU)中常见的一个保护机制,旨在提高系统的可靠性和安全性。它通过监视时钟信号的状态来确保系统始终有一个可靠的时钟源。如果检测到时钟失效或者不稳定的情况,CSS 可以自动切换到备用时钟源,甚至复位系统以避免潜在的问题。在这里我们可以看到在HSE(主时钟)出现问题的时候可以使用HSI或PLL。

接下来我们看两种时钟总线APB和AHB

在 STM32 微控制器系列中,APB(Advanced Peripheral Bus)和 AHB(Advanced High-performance Bus)是两种主要的总线类型,它们分别承担着不同的任务和职责。

1.1 AHB 总线

AHB 总线是高性能总线,主要用于连接高性能组件,如中央处理器(CPU)、DMA 控制器、高速存储器接口等。AHB 总线的特点在于其高带宽和低延迟,非常适合需要频繁和高速数据交换的操作。在 STM32 设备中,AHB 总线通常用于连接如下组件:

- CPU:如 Cortex-M 系列处理器。

- DMA 控制器:用于无 CPU 干预下的数据移动。

- 高速 RAM/ROM 存储器接口:如 Flash 存储器和 SRAM。

- 高速外设接口:如以太网 MAC、USB OTG FS/HS 控制器等。

1.2 APB 总线

APB 总线则是针对低速外设设计的,它提供了一种经济高效的方案来连接那些不需要高速数据传输的外设。APB 总线分为 APB1 和 APB2,两者都继承了 APB 的优点,但 APB2 通常具有较高的最大频率。APB 总线通常用于连接如下类型的外设:

- 定时器:如通用定时器、高级控制定时器等。

- 串行通信接口:如 UART、SPI、I²C 等。

- 模拟外设:如 ADC(模数转换器)、DAC(数模转换器)。

- 电源管理及低功耗相关外设:如独立看门狗定时器、窗口看门狗定时器等。

在 STM32 微控制器中,AHB 总线和 APB 总线协同工作,形成了一个层次化的总线结构。AHB 负责高速数据传输的任务,而 APB 则专注于低速外设的连接。这种设计方法不仅提升了系统的整体性能,也有效地平衡了系统成本和功耗。

接下来我们看几个特殊的时钟输出

- IWDGCLK: 独立看门狗(Independent Watchdog)的时钟源,通常来源于 LSI 。看门狗是一种避免系统进入死循环的手段,通过不断喂狗(刷新看门狗计时寄存器)表明系统正常。

- ADC Prescaler: ADC(模数转换器)的分频器,调整供给 ADC 的时钟频率。

接下来我们简单介绍一下其他输出

用于同步USB时钟

USB Type-C 连接器的引脚 D+ 和 D- 用于数据传输,这两个引脚同时也是用于同步时钟的关键部分。在 USB 通信中,D+ 和 D- 引脚上的信号包含了数据和时钟信息,接收方可以从这些信号中恢复出时钟信号,以便正确地解码数据。

用于AHB总线上的内存、DMA等(数据转移寄存器)

“to Cortex System timer” 时钟路径用于驱动系统计时器,帮助实现时间相关的功能。

“FCLK Cortex free running clock” 时钟路径用于提供处理器核的基本时钟信号,确保处理器及其周边模块的正常运行。